Samsung อาตผลิตชิบขนาด 3 นาโนเมตรในสัปดาห์หน้า ซึ่งจะเป็นการผลิตเชิงสำหรับวางขายในเชิงพาณิชย์ไม่ใช่ผลิตเพื่อการวิจัยและพัฒนา โดยหากข่าวลือดังกล่าวเป็นจริงจะหมายความ Samsung จะแซงหน้า TSMC ในการผลิตชิบด้วยเทคโนโลยีใหม่ ที่บริษัทหลังมีแผนผลิตชิบ 3 นาโนเมตรภายในครึ่งหลังของปีนี้

ชิบขนาด 3 นาโนเมตรของ Samsung จะมีพื้นที่ลดลง 35% มีประสิทธิภาพเพิ่มขึ้น 30% หรือประหยัดพลังงานลง 50% เมื่อเทียบกับชิบขนาด 5 นาโนเมตรนั่นเอง (ขนาดเดียวกับที่ผลิตชิบ Snapdragon 888 และ Exynos 2100)

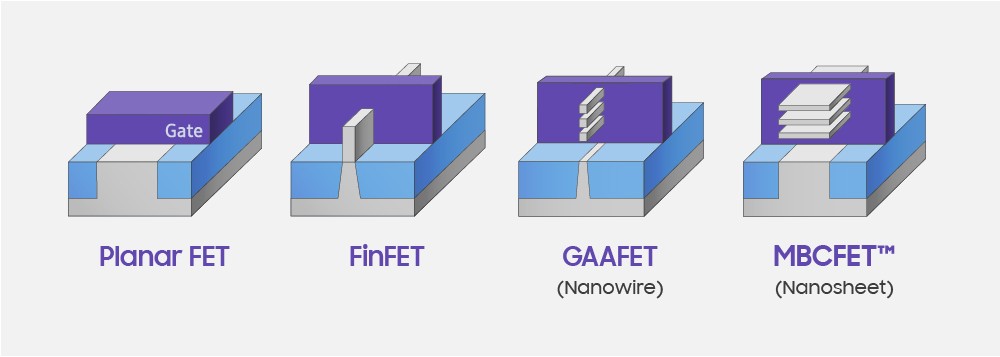

Samsung ทำเช่นนี้ได้โดยใช้การออกแบบทรานซิสเตอร์แบบ Gate-All-Around (GAA) ซึ่งเป็นขั้นต่อจาก FinFET ในการลดขนาดทรานซิสเตอร์โดยไม่กระทบต่อประสิทธิภาพการจัดเก็บกระแสไฟฟ้า

อย่างไรก็ตามสิ่งที่น่ากังวลสำหรับ Samsung คือผลตอบแทนจากการผลิตชิบ เพราะเมื่อเดือนตุลาคมทางบริษัทเผยว่าผลตอบแทนของชิบขนาด 3 นาโนเมตรเข้าใกล้ระดับเดียวกับการผลิตชิบขนาด 4 นาโนเมตร ที่คาดการณ์ว่าผลตอบแทนในการผลิตชิบดังกล่าวเป็นปัญหาของบริษัทพอสมควร

ทั้งนี้ชิบขนาด 3 นาโนเมตรในรุ่นที่ 2 หรือรุ่นอัพเกรดคาดว่าจะถูกผลิตในปีหน้า นอกจากนั้นจาก roadmap ของบริษัทระบุว่าการผลิตชิบขนาด 2 นาโนเมตรที่มีดีไซน์แบบ MBCFET จะเกิดขึ้นในปี 2025